# Deep Trench Guard Technology to Suppress Coupling between Inductors in Silicon RF ICs

Cheon Soo Kim, Piljae Park, Joung-Woo Park, Nam Hwang, and Hyun Kyu Yu

Microelectronics Technology Lab., Electronics and Telecommunications Research Institute,

161 Kajong, Yusong, Taejon 305-350, Korea

E-mail : cskim@etri.re.kr

**Abstract--** Trench guard technology was proposed to suppress the coupling between inductors, and to reduce cross talk in silicon RF ICs. The test structure adopting deep trench guard ring showed the coupling less than -40 dB in the frequency range of 0.5~20 GHz, and negligible change on designed inductance value up to 10 GHz. Furthermore, it can be also used to isolate a noisy circuit block from other quiet blocks in mixed signal silicon RF ICs.

## I. INTRODUCTION

Recently, RF transceiver circuits become more and more complex to meet the users' demands of dual-band (Cellular/PCS) or dual-mode (CDMA/ AMPS) operation of handsets [1-3]. To meet the functions in a single chip, the transceiver should be highly integrated or should be operated at wide-band. For a compact size transceiver IC, the electro-magnetic coupling between two adjacent inductors also should be controlled. Much works on coupling in silicon substrate have been published [4-7]. Diffusion guard ring is widely used technique in silicon ICs to reduce the substrate coupling through the spiral inductor [4], and also to prevent substrate noise in mixed signal circuits [5]. Well-designed guard ring can suppress the coupling efficiently at lower frequency below 1 GHz, but it is useless at high frequency above 3 GHz [6]. Ground shield pattern under the inductor also well known method to suppress the coupling and to improve the inductor quality [6]. It also has the problems of degrading the self-resonance frequency due to the increase of parasitic capacitance. The increase of substrate resistivity up to 2 k $\Omega$ -cm can suppress the coupling effectively compared with that of low resistivity substrate, but it also useless in the closely spaced inductor pairs [8]. Therefore, special techniques should be needed to solve the coupling

problems for designing a single chip CMOS or BiCMOS transceiver.

In this work, we proposed deep trench guard technology to suppress the coupling between inductor through the substrate. Trench guard technology showed a good isolation characteristics of a less than 40 dB in the frequency range of 0.5~20 GHz, and negligible change on the original designed inductance value. Moreover, it can be also used to isolate a noisy circuit from other quiet blocks in mixed signal silicon RF ICs.

## II. DEEP TRENCH GUARD RING DESIGN AND FABRICATION

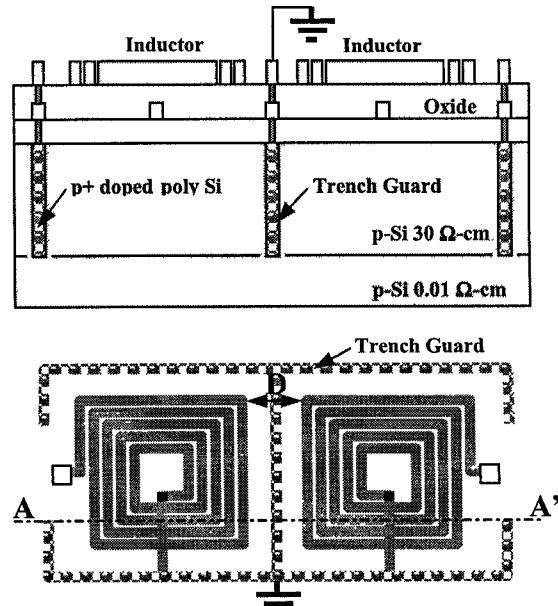

Fig. 1 Cross-sectional and top view of deep trench guard design. Each inductor was designed with the 60 $\mu$ m inner diameter and 8-turns with the inductance of 13 nH.

Several pairs of inductors with the variation of separation were designed to analyze the coupling through the substrate. Inductor pair was wired for two-port S-parameter measurement, and the degree of coupling between inductors was indicated by  $S_{21}$  parameter. To suppress the substrate coupling, deep trench guard was designed around the each spiral inductors as shown in Fig. 1, and diffusion guard was also designed for comparison.

Test structure was fabricated on silicon p+/p- epilayer substrate using the trench and NMOSFET technology. Silicon substrate was etched with a depth of 10  $\mu\text{m}$  and refilled with p+ doped poly-silicon to form the high conductive ground, and the surrounding ground was also connected to high conductive substrate (0.01  $\Omega\text{-cm}$ ) via trench bottom. After the formation of trench guard, spiral inductor was fabricated by using the two-layer metalization process (see Fig. 2).

Fig. 2 Cross-sectional view of deep trench and photo micrograph of the fabricated test chip. Trench depth and width was 10  $\mu\text{m}$  and 1  $\mu\text{m}$ , respectively

### III. MEASUREMENT RESULTS AND DISCUSSIONS

#### 1) The Effect of Guard Ring Technology

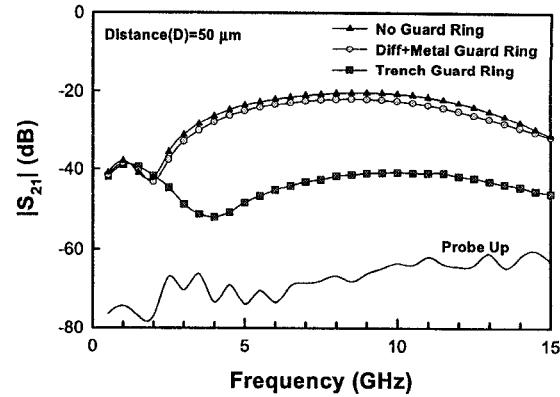

Fig. 3 shows the frequency response of  $S_{21}$  in a two adjacent inductors. It clearly shows that the coupling can be suppressed below -40 dB by adopting the deep trench guard in the frequency range of 0.5~15 GHz, and diffusion guard technique showed the negligible effect compared with that of without guard case. The  $S_{21}$  of 20 dB was reduced compared with that of no guard by adopting the trench guard in the frequency higher than 3 GHz. Therefore the deep trench guard showed a excellent isolation characteristics against coupling through the substrate. The test structure showed a small resonance peak at about 1 GHz, and it similar with the result [6].

Fig. 3 The frequency response of coupling with the variation of guard ring technology. Test structures were the identical geometry except guard ring.

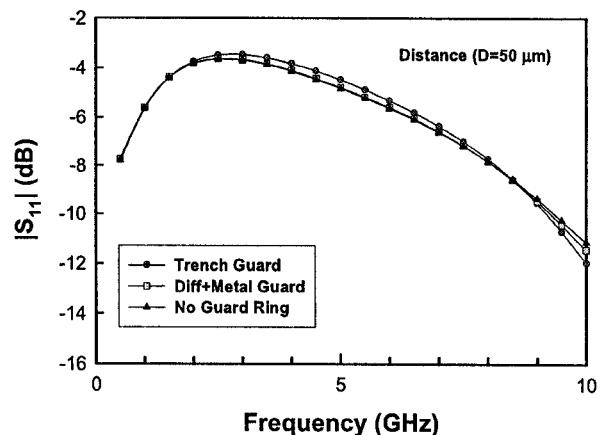

It is well known fact that the guard around the inductor changes the original designed inductance value because of the induced image current in guard ring [4]. However, the discontinuous deep trench guard which is designed around the inductor with the separation of 25  $\mu\text{m}$  showed negligible effect (below 3%) on  $S_{11}$  as shown in Fig.4. The  $S_{11}$  is directly related with an inductance value.

Fig. 4 Measured  $S_{11}$  of test structure with the various guard ring technology.

#### 2) The Effect of Physical Distance and Substrate

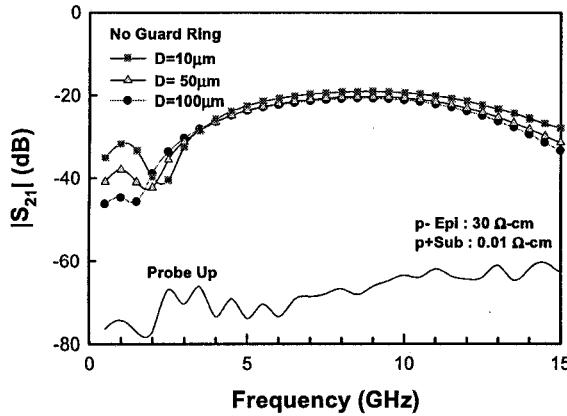

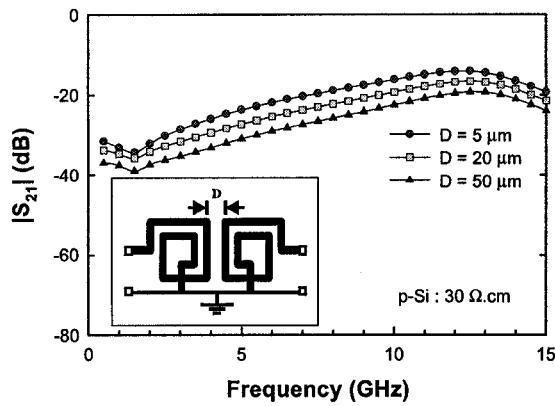

Electromagnetic coupling of inductor pairs is linearly depends on the distance and substrate conductivity, but in a heavily doped substrate, physical separation can't reduce the coupling as shown in Fig. 5. In case of non epi-

substrate the coupling is clearly reduced with the increase of separation distance as shown in Fig. 6. Therefore, it can be concluded that the main coupling path in epi-substrate is low conductive substrate below epi layer.

Fig. 5 The frequency response of coupling with the variation of physical separation on p+/p- epi-substrate.

Fig. 6 The frequency response of coupling with the variation of physical separation on p- non epi-substrate.

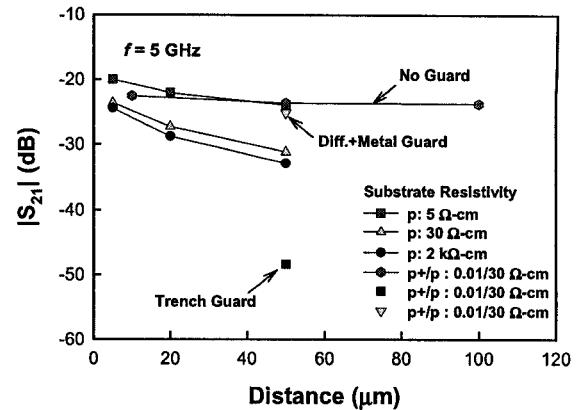

Fig. 7 shows the magnitude of coupling with the variation of substrate type, resistivity and distance. The deep trench guard technology can suppress the coupling to  $-50$  dB at the frequency of  $5$  GHz, which is a  $20$  dB lower than the case of high resistivity substrate ( $2$  k $\Omega$ -cm). As we previously studied [8], the inductor coupling also depends on geometry (number of turns), the quality factor as well as the substrate resistivity. Thus it is very complicate to establish the design rules for suppression the coupling by using the conventional guard technology. To solve this

problem, a strong coupling suppression technique should be needed for L-, C-, and X-band silicon RF ICs application. The proposed deep trench technology is a good promising candidate for the solution. Furthermore, it can be also used to isolate noisy power amplifier circuit and digital block from other quite analog blocks in a one-chip transceiver. The chip area consumption by using the trench technology can be minimized by the reducing trench open below  $1$   $\mu$ m.

Fig. 7. The  $S_{21}$  of two adjacent inductors with the variation of substrate type, physical separation, and guard ring technology.

The magnitudes of coupling with the variation of design technique and process technology were compared and summarized in table 1 at the frequency of major concern.

#### IV. CONCLUSIONS

We proposed trench guard technology to suppress the coupling between inductors and cross talk in silicon RF IC. The technology showed good isolation characteristics of less than  $40$  dB in the frequency range from  $0.5$  GHz to  $20$  GHz, and with negligible change on designed inductance value. Various experimental results showed no clear solution could be found for suppression the coupling by conventional guard technology except the deep trench technology. Furthermore, it can be also used to isolate the noisy power amplifier or digital block from quiet analog circuit block.

[Table 1] Summary of coupling with the various design technique and process technology at the frequency of major concern.

| Substrate type                                                                                                                                                                                     | Guard Ring | D (μm) | Magnitude of Coupling (dB) |       |       |        |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|----------------------------|-------|-------|--------|--------|

|                                                                                                                                                                                                    |            |        | 1 GHz                      | 2 GHz | 5 GHz | 10 GHz | 15 GHz |

| Si: p+/p-<br>0.01Ω-cm<br>30 Ω-cm                                                                                                                                                                   | Trench     | 50     | -40.1                      | -41.7 | -43.4 | -40.8  | -47.2  |

|                                                                                                                                                                                                    | Diff/Metal | 50     | -38.5                      | -43.2 | -25.1 | -22.5  | -31.8  |

|                                                                                                                                                                                                    | Metal      | 50     | -38.6                      | -42.5 | -23.9 | -21.7  | -30.8  |

| Si: p+/p-<br>0.01Ω-cm<br>30 Ω-cm                                                                                                                                                                   | No         | 10     | -31.7                      | -39.8 | -22.5 | -19.4  | -27.8  |

|                                                                                                                                                                                                    | No         | 50     | -38.0                      | -42.3 | -23.6 | -20.7  | -31.4  |

|                                                                                                                                                                                                    | No         | 100    | -44.7                      | -38.8 | -23.7 | -21.2  | -33.3  |

| Si: 5 Ω-cm                                                                                                                                                                                         | No         | 5      | -30.0                      | -25.6 | -20.0 | -21.8  | -24.5  |

|                                                                                                                                                                                                    | No         | 20     | -32.5                      | -27.9 | -22.0 | -23.6  | -25.8  |

|                                                                                                                                                                                                    | No         | 50     | -36.9                      | -28.5 | -24.0 | -26.1  | -30.6  |

| Si:30 Ω-cm                                                                                                                                                                                         | No         | 5      | -32.8                      | -32.2 | -23.6 | -15.9  | -18.6  |

|                                                                                                                                                                                                    | No         | 20     | -34.5                      | -34.2 | -27.2 | -19.0  | -20.7  |

|                                                                                                                                                                                                    | No         | 50     | -37.3                      | -37.7 | -31.2 | -22.3  | -23.0  |

| Si:2 kΩ-cm                                                                                                                                                                                         | No         | 5      | -31.6                      | -37.2 | -24.4 | -14.6  | -17.9  |

|                                                                                                                                                                                                    | No         | 20     | -33.2                      | -40.2 | -28.7 | -17.9  | -19.4  |

|                                                                                                                                                                                                    | No         | 50     | -36.5                      | -44.6 | -32.9 | -21.3  | -21.0  |

| Inductor inner diameter : 60μm, 8-turn, Line/Space: 10μm/2μm, L= 13 nH.                                                                                                                            |            |        |                            |       |       |        |        |

|  Below -40 dB,  Below -30 dB |            |        |                            |       |       |        |        |

## REFERENCES

- [1] M. Madihian, *et al.*, "CMOS RF ICs for 900MHz-2.4GHz Band Wireless Communication Networks," *IEEE RFIC Symposium Digest*, pp.13-16, June 1999.

- [2] Konstantina Rovos, *et al.*, "2.7 Volt Performance of High Dynamic Range Receiver ICs for Dual-Band CDMA Handsets," *IEEE RFIC Symposium Digest*, pp.73-76, June 1999.

- [3] K. Harrington, *et al.*, "Highly Integrated MMIC Upconverter/Drivers for Cellular and PCS CDMA Handsets," *IEEE RFIC Symposium Digest*, pp. 77-80, June 1999.

- [4] Alan L. L. Pun, *et al.*, "Substrate Noise Coupling Through Planar Spiral Inductor," *IEEE Journal of Solid State Circuits*, Vol. 33, No. 6. June 1998.

- [5] D. K. Su, *et. al.*, "Experimental Results and Modeling Techniques for Substrate Noise in Mixed-Signal Integrated Circuits," *IEEE Journal of Solid State Circuits*, Vol. 28, No. 4. April 1993.

- [6] C. Patrick Yue *et al.*, "On-Chip Spiral Inductors with Patterned Ground Shields for Si-Based RF IC's," *Symposium on VLSI Circuits Digest of Technical Papers*, pp. 85-86, 1997.

- [7] J. Burghartz, *et. al.*, "RF Circuit Design Aspects of Spiral Inductors on Silicon," *IEEE Journal of Solid State Circuits*, Vol. 33, No. 12. Dec. 1998.

- [8] C. S. Kim, *et al.*, "Design Guide of Coupling between Inductors and Its effect on Reverse Isolation of a CMOS LNA," *IEEE MTT-s Symposium Digest*, pp. 225-228, 2000.